二���、接收卡控制系統單元模塊設計

(一)時(shí)鐘控制模塊

1. 行計數時(shí)鐘和掃描控制信號

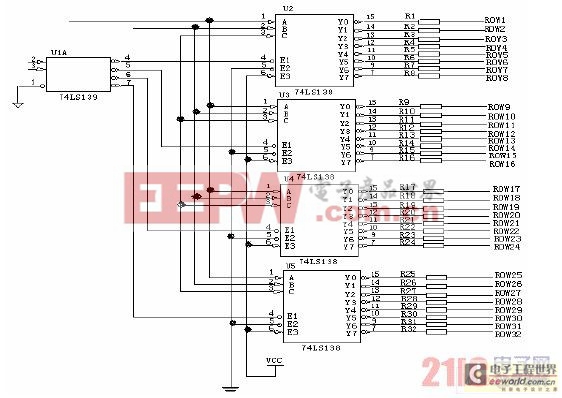

采用行掃描的��,必須產(chǎn)生行掃描控制信號�。如圖 2所示的row[4..0]是行掃描控制信號�,用它接一個(gè) 2-4 譯碼器和四個(gè) 3-8 譯碼器來(lái)產(chǎn)生 32個(gè)行選信號�����,構成 1/32 掃描方式的顯示屏��。Hclk為行計數時(shí)鐘�,也可以稱(chēng)為行鎖存時(shí)鐘����。

圖2 行驅動(dòng)模塊原理圖

評論