FPGA的機載合成孔徑雷達數字信號處理機接口板卡的

3.1 數據的打包和流向控制

雷達參數數據和原始回波數據的數據源是異步的,不能保證兩者確切的對應關(guān)系,接口板卡利用對緩存原始回波數據FIFO和緩存雷達參數數據雙口RAM的讀寫(xiě)控制,調整雷達參數數據和原始回波數據對應關(guān)系,將兩種數據源按處理機要求的輸入數據格式組成正確的數據幀雷達參數數據和原始回波數據打包后的數據幀格式如下:

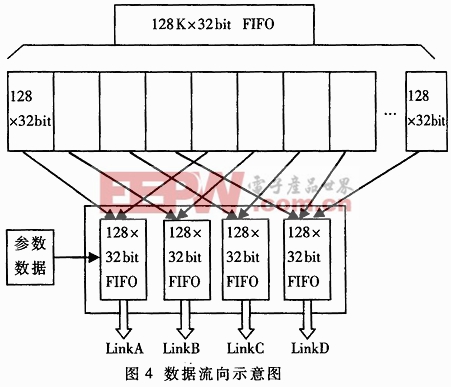

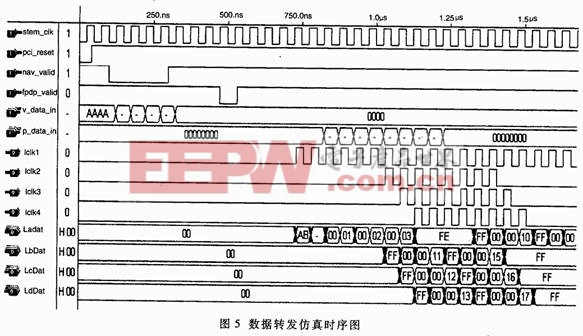

在程序中,設計了雷達參數發(fā)送控制計數器Para_counter和回波數據發(fā)送控制計數器Data_counter系統工作后,每次檢測到原始回波數據流的數據有效信號data_valid的上升沿(標記收到完整的一幀回波數據)時(shí),啟動(dòng)雷達參數發(fā)送控制計數器開(kāi)始計數,當計數到設定的值(本設計中為25)時(shí)停止計數并啟動(dòng)回波數據發(fā)送控制計數器開(kāi)始計數,計數到設定的值(本設計中為5000)時(shí)停止計數當檢測到原始回波數據流的數據有效信號data_valid的下降沿(標記開(kāi)始接收新的一幀回波數據)時(shí),兩個(gè)計數器都清零根據計數器的計數值產(chǎn)生Link口選擇信號確定數據的流向圖4給出了數據流向的示意圖圖5給出了基于MAXPLUSⅡ10.0的仿真結果,仿真顯示正確地實(shí)現了數據打包和流向控制

評論