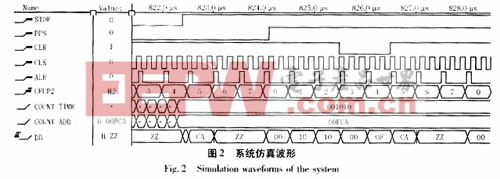

其仿真結果如圖2所示����。本文引用地址:http://dyxdggzs.com/article/150888.htm

4 結論

本文對高速數據采集系統中的采集數據貼上精確時(shí)間標簽的方法進(jìn)行了詳細地敘述和仿真��,得出如下結論:

(a) 假設高速AD轉換器件的轉換頻率為5MHz�,則本系統能為存入靜態(tài)RAM中的轉換數據貼上精度為0.2μs的時(shí)間標簽���。

(b) 通過(guò)復雜可編程邏輯器件(CPLD)間接地實(shí)現了“低速”的單片機系統對高速數據采集系統的實(shí)時(shí)監視��。

評論