Cadence Design System, Inc.宣布推出全新Modus?測試解決方案

針對測試設計過(guò)程中的挑戰,Cadence® Modus測試解決方案采用以下創(chuàng )新功能:

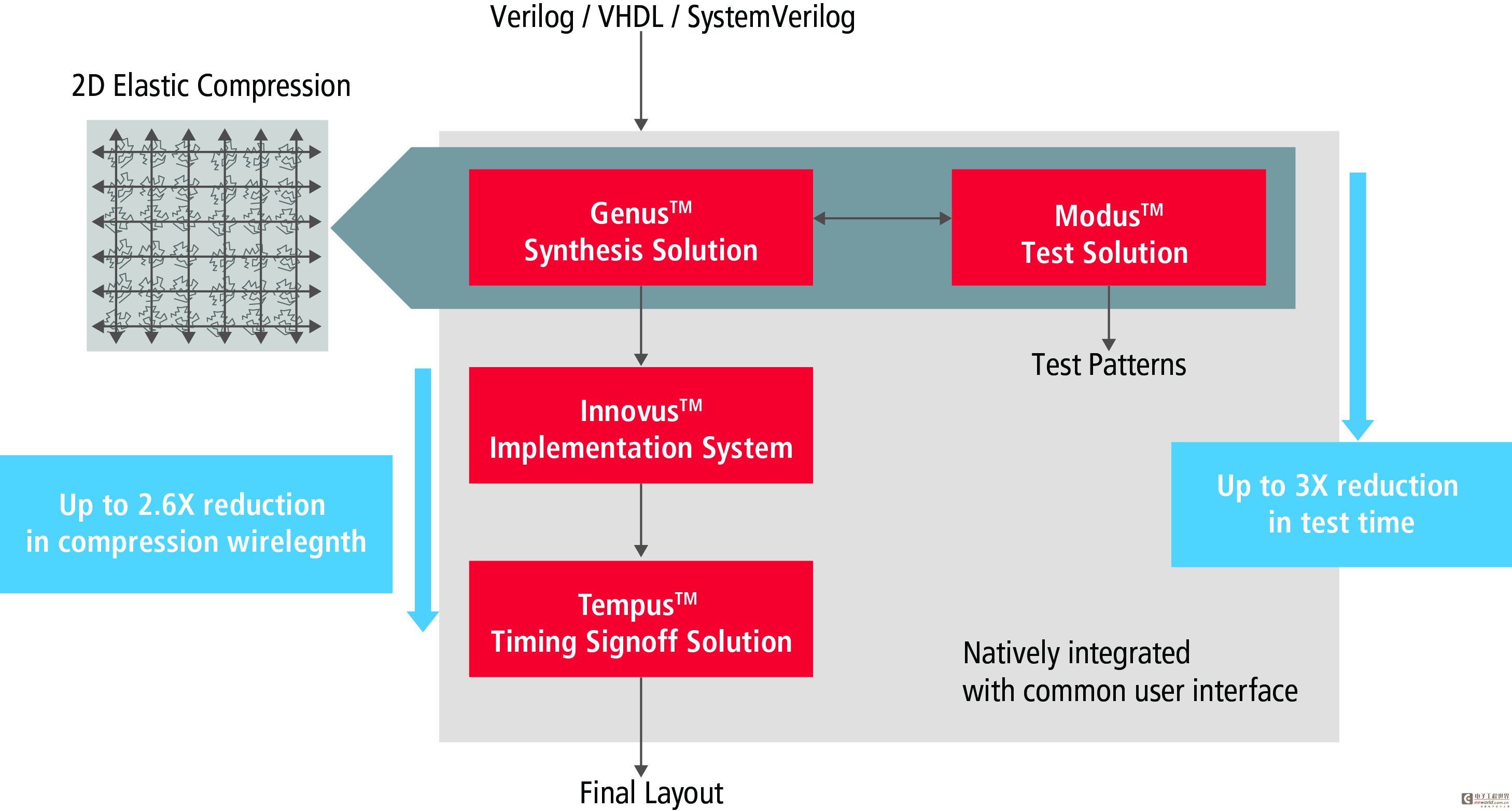

2D壓縮:掃描壓縮邏輯可在晶片平面布局上構成二維物理感知網(wǎng)格,從而提高壓縮比并縮短線(xiàn)長(cháng)。在壓縮比為100倍的情況下,2D壓縮線(xiàn)長(cháng)最高可比業(yè)內現行掃描壓縮架構縮短2.6倍。

彈性壓縮:在自動(dòng)測試模式生成(ATPG)期間,通過(guò)嵌入在解壓邏輯中的寄存器,按序控制多個(gè)掃描周期的關(guān)注數據位,確保壓縮比提高至400倍以上時(shí),仍可保持滿(mǎn)意的故障覆蓋率。

嵌入式存儲器總線(xiàn)支撐:插入共享測試訪(fǎng)問(wèn)總線(xiàn),同一IP核中的多個(gè)嵌入式存儲器可全速執行可編程存儲器內建自測試(PMBIST)。該功能還包括針對鰭式場(chǎng)效應晶體靜態(tài)隨機存儲器(FinFET SRAM)和汽車(chē)安全應用的全新可編程軟件測試算法。

強大的通用腳本和集成調試環(huán)境:可測性設計(DFT)邏輯插入及ATPG功能采用全新、且標準統一的TCL腳本語(yǔ)言和調試環(huán)境,兼容Cadence Genus™ 綜合解決方案、Innovus™ 設計實(shí)現系統及Tempus™ 時(shí)序簽核解決方案。

“Cadence新一代Modus測試解決方案采用全新的創(chuàng )新功能,可以從根本上改變設計和測試工程師解決測試問(wèn)題的方式。目前,我們正在為這項技術(shù)申請專(zhuān)利。”Cadence數字和簽核事業(yè)部高級副總裁兼總經(jīng)理Anirudh Devgan博士表示:“Modus測試解決方案通過(guò)搭建物理感知的2D網(wǎng)格架構,并按序壓縮測試模式(pattern),較傳統方法顯著(zhù)縮短了測試時(shí)間,為Cadence客戶(hù)帶來(lái)又一重要的盈利優(yōu)勢。”

評論