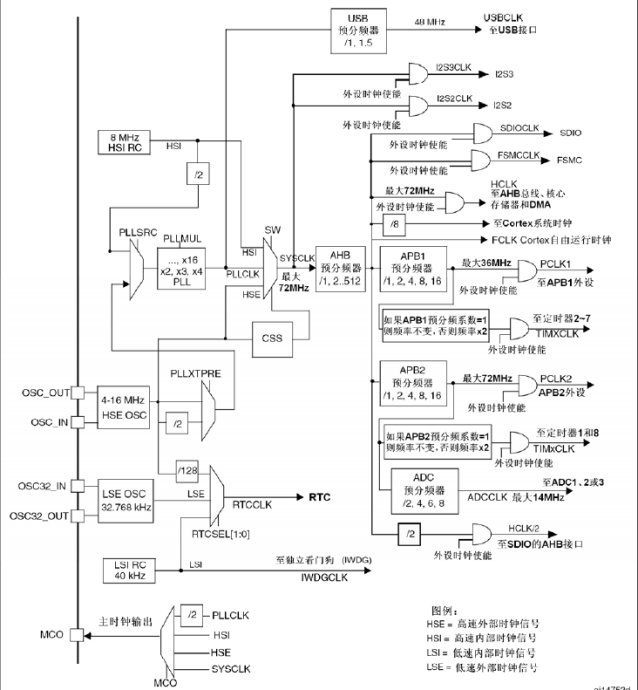

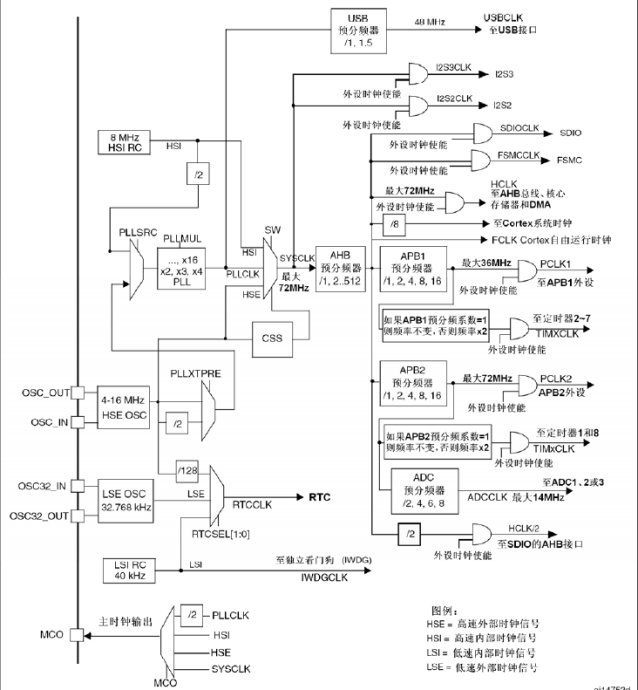

時(shí)鐘圖

本文引用地址:http://dyxdggzs.com/article/201611/321735.htm

//RCC_HSEConfig(RCC_HSE_OFF); // 關(guān)閉外部時(shí)鐘

//RCC_HSEConfig(RCC_HSE_ON);//開(kāi)啟外部時(shí)鐘

//RCC_HSICmd(ENABLE);// 開(kāi)啟內部時(shí)鐘

//RCC_HSICmd(DISABLE);// 開(kāi)啟內部時(shí)鐘

//雙高級外設總線(xiàn)結構:高速APB(APB2)速度達到72MHz��、低速APB(APB1)速度達到36MHz��。

//允許用戶(hù)優(yōu)化外設的使用(18MHz的SPI����、4.5Mbps的USART�����、72MHz的PWM定時(shí)器�、18MHz觸發(fā)I/O口)�����。

//RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_8); // 使用外部時(shí)鐘源F��,倍頻輸出等于 F*8/1

//RCC_PLLConfig(RCC_PLLSource_HSI_Div2, RCC_PLLMul_8); // 使用內部時(shí)鐘源F��,倍頻輸出等于 F*8/2

void RCC_Configuration(void)

{

RCC_DeInit();//將外設RCC寄存器重設為缺省值(即默認值)

RCC_HSEConfig(RCC_HSE_ON);//打開(kāi)外部晶振

if(RCC_WaitForHSEStartUp() == SUCCESS) //判斷起振是否成功

{

RCC_HCLKConfig(RCC_SYSCLK_Div1); //設置AHB時(shí)鐘(HCLK)(這時(shí)設置為=系統時(shí)鐘)

RCC_PCLK2Config(RCC_HCLK_Div1); //設置高速AHB時(shí)鐘(HCLK2)(這時(shí)設置為=HCLK)

RCC_PCLK1Config(RCC_HCLK_Div2);//設置低速AHV時(shí)鐘(HCLK1)(這時(shí)設置為=HCLK/2)

FLASH_SetLatency(FLASH_Latency_2);//設置FLASH存儲器延時(shí)時(shí)鐘周期數��。(設置為延時(shí)2個(gè)時(shí)鐘周期)

FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable);//使能預取指緩存

RCC_PLLConfig(RCC_PLLSource_HSE_Div1, RCC_PLLMul_9);//PLL的時(shí)鐘來(lái)源及倍頻的倍數

while(RCC_GetFlagStatus(RCC_FLAG_PLLRDY) == RESET) //檢測PLL是否就緒

{

}

RCC_SYSCLKConfig(RCC_SYSCLKSource_PLLCLK); //設置PLL為系統時(shí)鐘

while(RCC_GetSYSCLKSource() != 0x08) //檢測系統的時(shí)鐘源是否是PLL

{

}

}

RCC_APB2PeriphClockCmd(RCC_APB2Periph_USART1 | RCC_APB2Periph_GPIOA, ENABLE);//使能USART GPIOA時(shí)鐘

}

評論