GNU ARM匯編--(六)s3c2440的時(shí)鐘控制

不再發(fā)感慨了,下面就對s3c2440的時(shí)鐘做一個(gè)說(shuō)明,然后給出匯編對時(shí)鐘的控制代碼,最后比較一下有時(shí)鐘控制和沒(méi)時(shí)鐘控制下的流水燈的區別.

本文引用地址:http://dyxdggzs.com/article/201611/321725.htms3c2440的時(shí)鐘控制邏輯可以產(chǎn)生3個(gè)時(shí)鐘信號:用于CPU核(ARM920T)的FCLK,用于A(yíng)HB總線(xiàn)外設(存儲控制器中斷控制器LCD控制器DMAUSB的主機端)的HCLK和用于A(yíng)PB總線(xiàn)外設(比如WDT IIS I2C PWM timer MMC ADC UART GPIO RTC SPI)的PCLK.s3c2440有兩個(gè)鎖相環(huán),一個(gè)是用于FCLK HCLK PCLK的MPLL,一個(gè)專(zhuān)用與USB的UPLL.

首先看一下下面的表格:

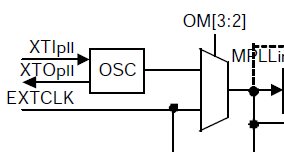

時(shí)鐘源可以來(lái)自于外部晶振(XTlpll)或者外部時(shí)鐘(EXTCLK).datasheet中的圖7-1顯示了時(shí)鐘的體系框圖,這里就不給出了,截出一小部分與上圖做個(gè)呼應:

這個(gè)圖就反映了OM[3:2]在XTlpll和EXTCLK之間的選擇.

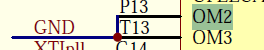

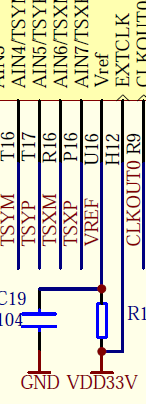

接下來(lái)看看TQ2440的原理圖是如何處理的:

從原理圖可以看出:OM[3:2]為00b,意味著(zhù)使用晶振來(lái)產(chǎn)生MPLL CLK和UPLL CLK.我們的XTIpll接的就是12M的晶振,這時(shí)候EXTCLK按照規定是要接高的,對應圖如下:

值得注意的是:盡管MPLL在reset后就開(kāi)始工作了,但是MPLL output只有在軟件寫(xiě)有效的設置值到MPLLCON寄存器后才作為系統時(shí)鐘的.在有效設置之前,外部晶振或者EXTCLK直接用于系統時(shí)鐘.哪怕是你不想改動(dòng)MPLLCON寄存器的初始值,你也得將該值寫(xiě)入MPLLCON.

上面的話(huà)意味著(zhù):如果不進(jìn)行時(shí)鐘的設置,那么我的板子就運行在晶振為12M的系統時(shí)鐘下,這個(gè)和s3c2440的400M相去甚遠,做流水燈的延時(shí)肯定也差數量級的,這個(gè)等會(huì )就可以看到.

Mpll = (2*m * Fin) / (p * 2^s)

m = M (the value for divider M)+ 8, p = P (the value for divider P) + 2

s3c2440支持FCLK HCLK和PCLK之間的分頻比的選擇.比例由CLKDIVN寄存器的HDIVN和PDIVN決定.可參見(jiàn)下表:

注意:CLKDIVN要小心設置,不要超出了HCLK和PCLK的限制.如果HDIVN不為0,要用下面的指令,CPU總線(xiàn)模式從Fast Bus Mode變?yōu)楫惒娇偩€(xiàn)模式:

MMU_SetAsyncBusMode

mrc p15,0,r0,c1,c0,0

orr r0,r0,#R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

下面開(kāi)始看看寄存器的設置:

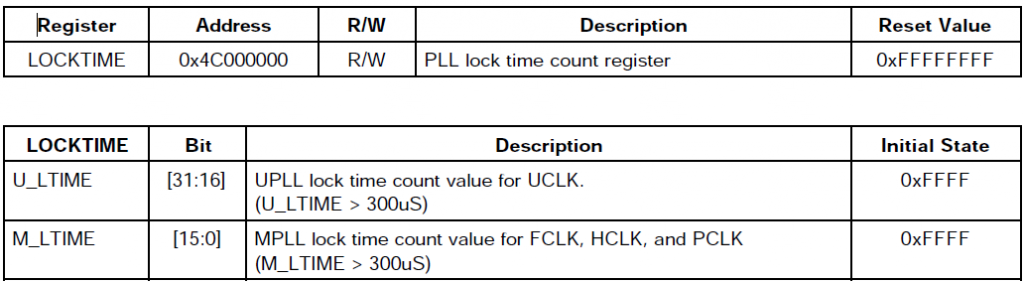

LOCK TIME COUNT REGISTER (LOCKTIME)

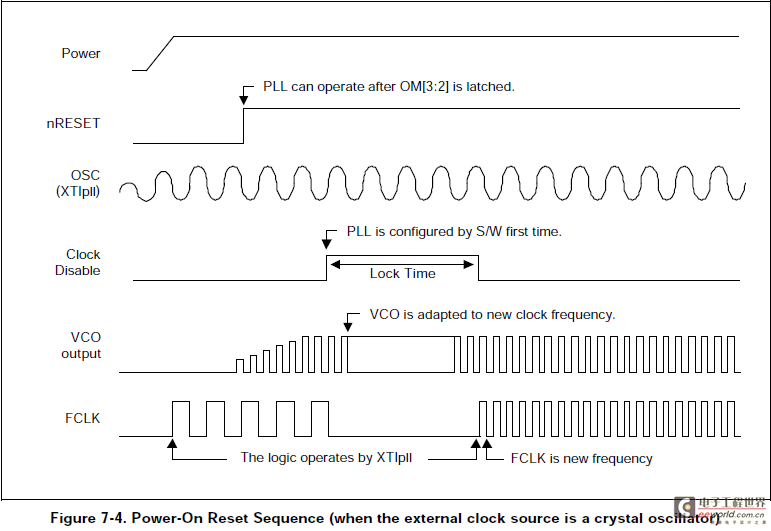

這個(gè)時(shí)間是要保證PLL輸出頻率穩定的,時(shí)序圖如下:

這個(gè)計數器的設置就是時(shí)序圖中的lock time,而在寄存器說(shuō)明中規定要大于300us,那么這個(gè)時(shí)候根據12M的晶振頻率,計算如下:

(1/12M)*N>300us 所以N>3600 所以可以用寄存器的默認值0xffff.

PLL CONTROL REGISTER (MPLLCON & UPLLCON)

MPLL Control Register

Mpll = (2 * m * Fin) / (p * 2S)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

UPLL Control Register

Upll = (m * Fin) / (p * 2S)

m = (MDIV + 8), p = (PDIV + 2), s = SDIV

評論