I2C總線(xiàn)串行輸入輸出結構

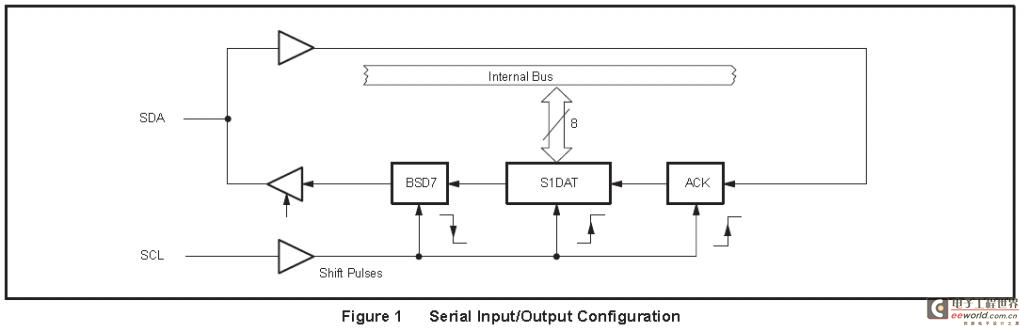

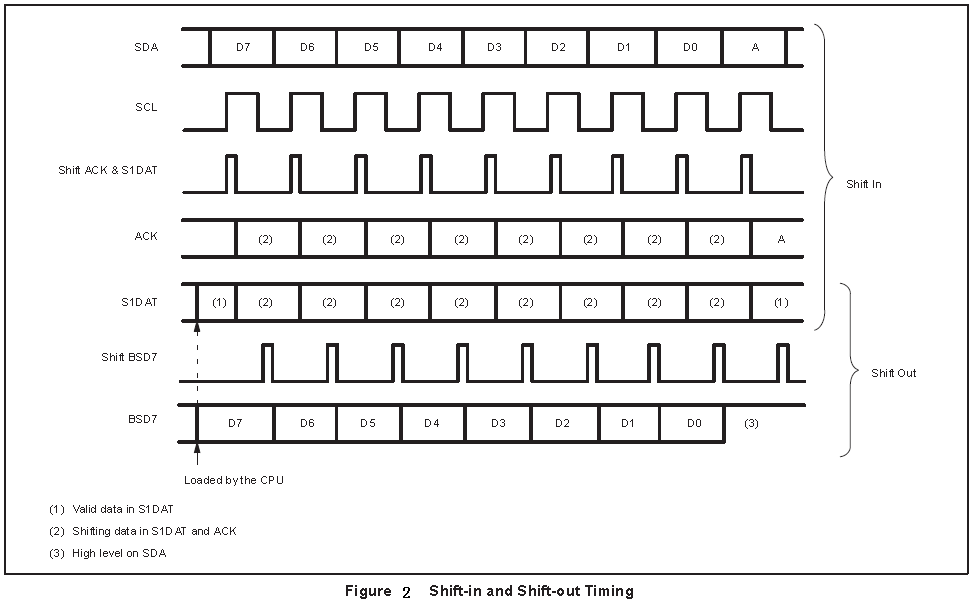

IIC總線(xiàn)的串行輸入輸出結構保證了IIC總線(xiàn)的數據寄存器中能保存總線(xiàn)上的最新數據。SDAT和ACK組成一個(gè)9為的移位寄存器,它組成一個(gè)環(huán)狀結構。串行輸出的同時(shí)不斷采入總線(xiàn)上的數據。ACK標志位由總線(xiàn)控制,并可以由CPU存取(存入1對應的是非應答,存入0對應的應答)。在SCL線(xiàn)上的時(shí)鐘脈沖的上升沿,串行數據通過(guò)ACK標志位存入SDAT,串行數據在SCL時(shí)鐘脈沖下降沿沿BSD7移出當一個(gè)字節數據移入SADT后,SDAT中的數據有效,控制邏輯在第9個(gè)時(shí)鐘脈沖周期送出應答位。

為什么IIC總線(xiàn)進(jìn)行數據發(fā)送時(shí),時(shí)鐘信號為高電平期間,數據線(xiàn)上的數據必須保持數據穩定???這是因為會(huì )在高電平期間采集總線(xiàn)上的數據,如果此時(shí)總線(xiàn)上的數據不穩定,會(huì )導致采集的數據和發(fā)送的數據不一致,從而關(guān)閉發(fā)送(類(lèi)似仲裁失敗)。協(xié)議規定只有在時(shí)鐘信號為低電平期間,數據線(xiàn)上的高電平或低電平才允許變化,這是因為BSD7中的數據是在時(shí)鐘下降沿發(fā)出的,且不會(huì )在時(shí)鐘脈沖低電平期間采集總線(xiàn)上的數據。

在CPU對SDAT寫(xiě)入時(shí),SDAT7裝入BSD7,這是向SDA線(xiàn)上發(fā)送的第一位數據,9個(gè)時(shí)鐘脈沖后SADT中的8位數據發(fā)送到SAD線(xiàn)上,應答位出現在A(yíng)CK中,這樣發(fā)送到總線(xiàn)上的數據又返回到SDAT中。

SDA寄存器,包含個(gè)待發(fā)送的數據或一個(gè)剛收到的數據字節,發(fā)送時(shí),數據總是從右向左移位。數據移出時(shí),總線(xiàn)上的數據同時(shí)移入,移位寄存器的這種結構保證了總線(xiàn)競爭失敗時(shí)數據不會(huì )丟失。它以并行的方式與內部總線(xiàn)相連,以串行方式與SDA相連。發(fā)送數據時(shí),由內部總線(xiàn)裝入到SDAT中,發(fā)送時(shí),數據以串行從串行通道返回SDAT中。接收時(shí),裝入新接收的SDA線(xiàn)上的數據。

評論